시놉시스가 29일(현지시간) 미국 캘리포니아 산타클라라에서 열린 연례 시놉시스 사용자 그룹 컨퍼런스에서 고급 디지털 및 아날로그 칩의 설계, 검증, 테스트 및 제조를 위한 인공지능(AI) 기반 도구 모음인 ‘시놉시스ai(Synopsys.ai)’를 발표했다.

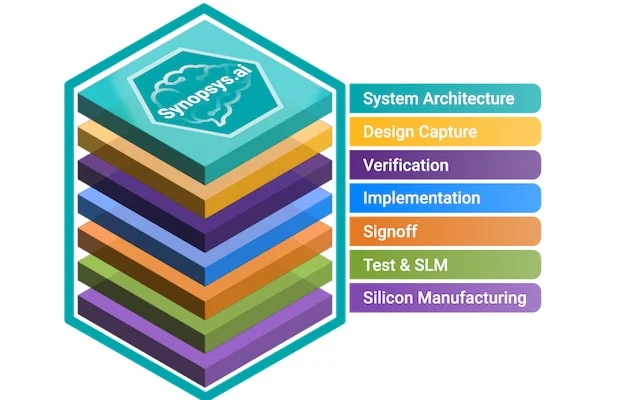

시놉시스ai는 엔지니어가 시스템 아키텍처 정의 단계, 설계 단계 및 제조를 포함한 칩 설계의 모든 단계에서 클라우드 기반 플랫폼을 사용해 AI를 활용할 수 있도록 한 도구다.

시놉시스는 전자 설계 자동화(EDA)의 선구자로서 칩 제조업체가 차세대 반도체를 정의, 계획, 설계, 구현, 검증 및 제조하는 데 필요한 소프트웨어, 하드웨어 및 서비스를 제공한다.

칩 메이커들은 고성능 컴퓨팅, 분석 및 AI 발전을 가속화하기 위해 점차 강력한 칩을 개발해야 하는 압력을 받고 있다. 특히, 인간과 유사한 챗봇, 수술 로봇 및 자율 주행 자동차와 같은 탁월한 발전은 AI가 주도하고 있다.

그 결과, 더 큰 칩 복잡도에 대한 수요는 꾸준히 증가하고 있다. AI는 이 수요를 충족하기 위해 필요한 더 강력한 칩을 제작하는 데 도움이 될 수 있다.

시놉시스는 시놉시스ai EDA 제품군이 기능 검증 및 실리콘 테스트를 위한 솔루션으로 칩 설계를 가속화하는 데 도움이 될 수 있으며, 이후 더 많은 기능을 추가할 예정이라고 발표했다.

아르빈드 나라야난 시놉시스 EDA 그룹 제품 라인 관리 수석 이사는 “AI가 고품질 칩을 구축하는 데 필요한 설계 공간 탐색, 검증 범위 및 회귀 분석, 테스트 프로그램 생성과 같은 많은 반복 작업을 처리하는 데 도움이 된다”고 설명했다.

이를 통해 엔지니어링 팀은 새로운 기능을 개발하고 제품을 차별화하는 등의 가치 있는 작업에 집중할 수 있다.

시놉시스ai는 자동 설계 공간 탐색을 위한 DSO.ai, 신속한 RTL(Register-Transfer Level) 검증 및 버그 검출을 위한 VSO.ai, 그리고 실리콘 테스트 과정 자동화를 위한 TSO.ai로 구성된다.

시놉시스는 디지털 칩이 동작할 수 있는 설계 공간의 수가 거의 무한하기 때문에 AI가 분명한 이점이 있다고 주장한다.

VSO.ai의 사용은 검증 과정을 활성화시켜 시간을 절약하고 테스트에서 높은 효율을 보장한다.

TSO.ai는 자동 테스트 패턴 생성 도구를 사용해 새로운 칩 설계의 결함 범위, 패턴 수, 런타임을 자동으로 평가한다.

샹카르 크리슈나무티 시놉시스 EDA 그룹 총괄 매니저는 “복잡성, 엔지니어링 리소스 제한 및 타이트한 납기에 대한 고민으로 AI 기반 EDA 소프트웨어 스택에 대한 수요가 증가하고 있다”면서 "시놉시스ai 기술을 사용하면 고객은 다양한 도메인에서 설계 솔루션 공간을 빠르게 탐색할 수 있으며, AI가 이전 실행에서 학습하면서 최적의 결과를 훨씬 더 빠르게 찾을 수 있다. 이것이 고객이 어려운 설계 및 생산성 목표를 달성하도록 변화시키고 있다"라고 설명했다.

시놉시스는 시놉시스ai 제품군이 세계에서 가장 큰 10개 반도체 회사 중 9개에서 채택되었으며, 이를 이용한 고객들은 검증 생산성이 10배 향상되고 실리콘 테스트 비용이 감소해 제품 개발 기간을 줄이고 비용을 절감할 수 있었다고 밝혔다.

또 크리슈나무티는 AI 챗봇을 통해 보다 정교한 방식으로 엔지니어 고객을 지원하는 기능에 대해서도 "우리는 포트폴리오에 이러한 많은 기술을 통합하는 것을 포함하는 로드맵을 가지고 있다"고 언급했다.

박찬 위원 cpark@aitimes.com